AS7C1026B Overview

Key Specifications

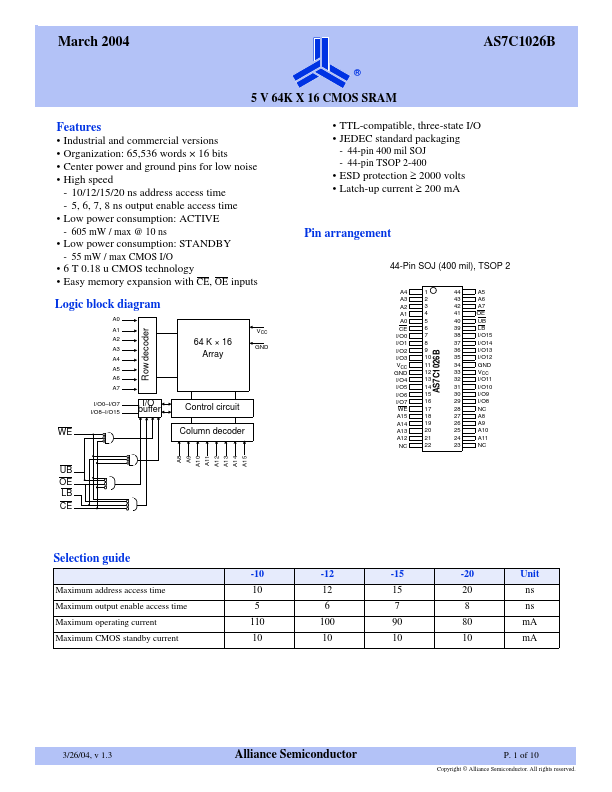

Package: TSOP

Pins: 44

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Key Features

- Industrial and commercial versions

- Organization: 65,536 words × 16 bits

- Center power and ground pins for low noise

- 10/12/15/20 ns address access time

- 5, 6, 7, 8 ns output enable access time